IDF 2010でSandy Bridgeが大々的にアピールされたところだが、今を遡ること約10年。CPUコアにメモリコントローラ、グラフィックスを統合したIntelプロセッサがあった。しかし、それは様々な理由で製品として出荷されることはなかった。それがIntel Israelが設計したTimnaである。プロセッサレベルでの失敗とは言えなかったTimnaだが、捲土重来。Banias(Pentium M)をひっさげ、Intel社内での地位向上を果たし、ついにCoreマイクロアーキテクチャへ昇華したことで、Mobileという1ジャンルからメインプロセッサへの道に進んだ。そして、統合プロセッサの夢よ再びという事で登場するのが Sandy Bridgeである。数々の失敗と成功を経た成果を見る前に、かつて今以上に拙い私がXWIN II Web Pageに書いたTimna関係の記事を振り返ってみようという企画である。

この文以下は、10年前の2000年に書かれたものなので、そのあたりを踏まえてご覧いただこう。

巻頭言 193「Timna」

Intel社は現地時間2月15日、次世代IA-32 ProcessorであるWillametteについて発表を行い、サンプル版のWillametteを1.5GHz(=1500MHz)という動作周波数でデモを行い、近くの会場でThunderbirdでIDFを出し抜こうとしていたAMD社の度肝を抜きました。と、昨日ふれたように、大手PCマスメディアはこぞってこのニュースを取り上げています。AMD社のThunderbird 1.1GHzデモは、先月のISSCC 2000の時のようには注目もされなかったようです。

ですが、Willametteよりも重要なプロダクツがあわせて発表されている事実も見逃せません。そのコードネームはTimna。S3社のビデオテクノロジ提供を受けたとされる統合Processor(Chipset)です。このTimnaは位置付け的にはCeleronの後継を担うとされており、場合によってはCeleronブランドが消えてなくなるほどのインパクトを持ったものだといえます。これまでのPCを構成する主要チップセットはこのようになっていました。

- Processor + Video + MCH + ICH (i820の場合)

- Processor + MCH&GCH + ICH (i810eの場合)

- Processor + Video + NorthBridge + SouthBridge (440BXの場合)

- Mobile Processor + Video + 440MX (440MXの場合)

これがTimnaを採用すると、

- Timna + ICH (Direct Rambus DRAM仕様の場合)

- Timna + ICH + MTH (SDRAM仕様の場合)

(Timna = Processor + Video + MCH)

のようにチップ構成が4チップから最小2チップ構成とすることができるわけです。もともと、TimnaはIntel社のDirect Rambus DRAM移行計画に従って、i820チップセットのMCH(Memory Controller Hub)のサブセットをProcessorに統合した関係上、メモリインタフェースがDirect Rambus DRAMに特化したものとなっているため、本来の構成は2チップ構成で済む予定だったものが、IDFで公開されたTimna搭載超小型マザーボード「Cape Arago」では3チップ構成となってしまっています。この3チップ構成という形では、Video機能(GCH)をチップセットに統合したi810や i810eそして近いうちに登場するi815と変わらず、やはり、Direct Rambus DRAMの躓きがここにも表れていると読み取ることができます。

それはともかく、TimnaのSDRAMバージョンがもし登場したなら(i820のサブセットでなく、i815のサブセットを統合したならということ)、 Timnaの存在価値は飛躍的に高まるでしょう。ProcessorとしてはCoppermineコアを採用しているので、演算性能は当面の間は問題なく、ICHを切り離したことで、次世代ATAインタフェースの取り込みも容易になっているのですから、低価格版としての位置付けとしても素直なSDRAM バージョンTimnaは求められており、それは実製品が登場する今年秋に間に合うようであれば、Celeronを完全に置き換えるものとなるでしょう。

でも、そうなってしまってはCeleronでのオーバクロックという楽しみは消えてしまうのか? Videoはおそらく切り離しさせない仕様となるのは明白で、高機能Videoを訴求する場合には、上位Processorをお求めくださいというのが仕様となることでしょう。これは差別化が難しかった廉価版Processorと通常版Processorとの差を作り出すには格好の仕様に見えるからです。(2000/2/17)

巻頭言 242「Timnaの理想と現実」

以前、巻頭言193でTimnaを取り上げたことがありましたが、今回、改めてTimnaについて見て行きたいと思います。

Timnaとは、Intel社がヴァリューPC向けに提供するチップセット統合Processorのコードネームです。今年秋頃出荷予定で、2月のIDF で一般に公開されたプロダクトです(以前の巻頭言もこのタイミングで取り上げました)。Timnaの目標は、低価格化だけでなくPCを構成するチップ数の削減により、実装面積を減らすことも大きなものとなっています。

では、Timnaを採用した理想的なPCのブロック図を掲げましょう。

理想的なTimna PCは、ブロック図にはビデオメモリの存在をありにしていますが、UMAを利用することでメインメモリをビデオメモリとしても使用できるため、これも不要になります。そうなると、Timna、ICH、DRAMのみで主要チップが構成できてしまうことがおわかりになると思います。これ以外に必須となるであろう、サウンドやモデムについても、AC'97に対応することで事実上インタフェースだけを用意すればよいので、CyrixのMediaGXを髣髴させる、あるいはそれ以上の統合チップセットだということができます。

しかし、Intel社にとって厳しい現実は、メモリサブシステムをDirect Rambus DRAMとしてしまったことです。言うまでもなく、Direct Rambus DRAMは大変高価であり、今でも128MB RIMMが一つ8万円前後という価格であり、この価格だけでヴァリューPC一台分以上なのでお話になりません。このため、Timnaを設計変更することなく、メモリサブシステムを変えるのは(Direct Rambus DRAMからSDRAMへ)、他のDirect Rambus DRAMをメモリサブシステムとしてしまったi820等と同様、82805AA(Memory Transfer HUB、MCH)を利用しなければならなくなってしまいました。2月のIDFでも、展示されたTimnaシステムはMCHを搭載していた事実がこれを裏付けます。

現実は、メモリサブシステムだけの変更だけではありません。未だ、レガシーフリーPCを完全に実現できていないこともあって、すべてをICHが掌ることができず、Super I/Oチップを利用しなければならないでしょう。USB接続のプリンタなども多く出てきていますが、完全に移行することはまだまだでしょう。OSも Windows Meといったものが出てこなければならないということもありますし……。

Timnaの最大の問題点はメモリサブシステムにあるのは疑いがないところです。メモリサブシステムを変更したTimnaの登場も、可能性としては高いと思われます。また、レガシーフリーPCの尖兵として、X-Boxというものもあるでしょう。本当の意味でのホームPCには、このようなTimnaのようなテクノロジが次々と出てこなければならないと感じるのですね。(2000/4/3)

巻頭言 284「Timnaに赤信号? MTHのリコール問題」

Intel社は現地時間10日、「Intel To Replace Motherboards With Defective Memory Translator Hub Component」(日本語版は11日付で「インテル 欠陥のあるメモリ・トランスレータ・ハブ搭載のマザーボードを交換」)という発表を行い、i820チップセットとSDRAMの組み合わせの際に必要となるMTH(Memory Translator Hub)こと82805AAのリコールをするとしました。

MTHは上図のとおり、本来、Direct Rambus DRAMのみをサポートするi820にPC100 SDRAMを接続するためのサポートチップです。その役割は、PC100 SDRAM信号をDirect Rambus DRAMの信号に相互変換(i820が受け入れられるよう)するものです。建前上、MTHは、これまでのSDRAMという資産を新しい環境でも生かせるようにということで用意したことになっていますが、実際はDirect Rambus DRAMの普及が遅々として進まず価格が非常に高いということで、やむなく登場したであろうことはチップの型番から想像できます(ハイエンドである i840のMRHが82803AAと82804AAという型番)。このように急場しのぎの登場が仇となったのか、表記のようにMTHはリコールの対象となってしまいました。

このMTHを搭載したマザーボードは、DIY用のマザーボードはいくつか見られるものの(基本的にi820チップセットでSDRAM搭載可能なものは全て)、それほど主流とはなっていないし(一部ショップブランドではそれなりの位置付けにしていたところも散見できたが)、影響はあまり大きくないように見られます。ですが、MRHのリコール問題は、Intel社の将来計画に大きな影を落とすものとなるのです。

それがコードネームTimnaと呼ばれる統合Processorの行方です。

Timnaシステムは、言ってみればProcessorとi820のサブセット、そしてグラフィックスを統合したもので、メモリサブシステムとしては Direct Rambus DRAMしか考えられていません。しかし、i820と同様、いやそれ以上にTimnaの位置付けはローエンドPCなので、高価なDirect Rambus DRAMではお話にならないのは明白です(それだけ、開発当時はDirect Rambus DRAMに賭けていたわけだが)。そこで、TimnaシステムにもMTHがやむなく採用されたのですが、統合Processorの旨みは消えたも同然という評価が多くの声だったのは疑いない事実でした(CPU + 2 x Chipset = CPU + Chipset + MCH ですから)。この声にもめげず、Intel社は上図のような形でTimnaシステムを推進しようという矢先、MCHのリコール問題が起こったのですから、まさに泣きっ面に蜂でしょう。

TimnaシステムにMCHが使えなくなったらどうなるか。メルコがDirect Rambus DRAMの大幅値下げを発表したというニュースも出たものの、今秋までにSDRAM並に価格が下がり、供給量が増えるということはないだろうから、Timnaシステムが本来の Direct Rambus DRAMにすることはできないでしょう。そうなると、MCHの改良という線ももちろんありますが、かなり後ろ向きのものであるので、なかなかそれもやりにくい。Timnaそのもののメモリサブシステムを変えるというのはさらに難しい(次のTimna+からはともかく)。

さて、次のIntel社の一手はどうなる? (2000/5/12)

巻頭言 407「Timnaのここが変わる?」

先週開催されたIDF(Intel Developer Forum Fall 2000)の話題で、Timnaについて徒然っていきたいと思います。

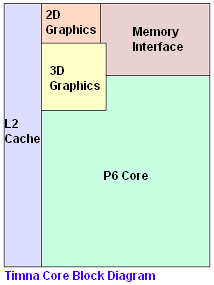

Timnaについて、最も注目すべき発表はTimnaのダイ写真が公表されたことでしょう。Timnaは、Processorコアにグラフィックス統合チップセットをさらに統合したものなので、巷ではダイサイズがそれなりの大きさと思われていましたが、さすがはIntel社のインプリメントチームです。なんと、Coppermineコアとほぼ同等のサイズでTimnaコアを実現したのです(もちろん、プロセスサイズを同等にして)。まずは、その Timnaのダイの模式図を下記に示しましょう。

Timnaには、最初にも書いたように、Processorコアとグラフィックス統合チップセットが一まとめになったものですが、機能的分類をすると、本来のProcessorコア部分、128KB L2キャッシュメモリ(以上、Processorコア)、メモリサブシステム、2D及び3Dグラフィックスエンジン(以上、統合チップセット)の5つに分けることができます。このうち、上図から分かるように最大面積を占めるものが「P6 Core」とある本来のProcessorコア部分なのですが、当然のことながら非常に小さいものとなっています(Timnaコア全体で Coppermineと同等なのだから)。とはいいつつ、IDFでの説明では腑に落ちない点があります。

それは比較対象としてKatmaiコアを例示していることです。説明では、TimnaコアのProcessor部分はKatmaiコアをベースとしているようですが、これはCoppermineコアだと、CeleronベースのCoppermine-128Kでも統合されているL2 Cacheは最低256KB以上実装されているために、L2キャッシュを除く本来のCoppermine Processorコアを比較の引き合いに出すと、大してサイズの縮小というものに対するインパクトが薄れるのではないかと思えるのです。ちょっと回りくどい言い方になってしまいますが、L2キャッシュが完全にProcessorコアから外されているKatmaiコアをベースにしたのは事実でしょうが、 Timnaコアに鎮座するProcessor部分はKatmaiコアのそれとはまったく異なったもので(設計手法の変更により、という説明はある)、 Katmaiをこれだけ小さくしたのだという技術者の誇示は分かるにしても、Processorベースで言うなら引き合いを現行のCoppermineに求めるのが当然でしょう。しかし、技術者の誇示とは別に敢えてKatmaiとしたのは、Timnaは小さいという印象を植え付けるためのプレゼンだという印象を強く受ける、というわけです。

さて、横道にそれてしまいましたが、TimnaもWillamette(Pentium 4)同様、Direct Rambus DRAMの影響を引きずっています。メモリインタフェースは、Direct Rambus DRAMのみがサポートされているため、Timna本来のターゲットとは相容れないことから、SDRAMベースまたはDirect Rambus DRAMとSDRAM両方のサポート、あるいはDDR SDRAMへの変更が示唆されています。Timnaにとってメモリサブシステムが重要なのは、グラフィックスを統合しているため、グラフィックス周りの処理も大きくメモリサブシステムの影響を強く受けるためです。Intel社の唯我独尊時代に計画されたTimnaですから、Direct Rambus DRAMのみというのは思想上から当然ですが、技術上からも大きなメモリ帯域幅を必要とするわけです。仮にいくらグラフィックスエンジンが強化されたとしても、メモリサブシステムが脆弱なままではそれを生かすことはまったくできないことは、昨今のデスクトップ向けビデオカードが次々とDDRを採用していることからも明らかでしょう(また、その次としてビデオメモリ統合がある)。

目先のことを言えば、Memory Protocol Translator(MPT)を経由したPC100 SDRAMではパフォーマンスに難があり、チップ数縮小を目指していた結果にも応えられない(この辺の議論は、半年ほど前の巻頭言でも展開しています)ということがありますが、Timnaの本質的問題はバスにあります。とはいいつつ、統合によるメリットであまり性能が向上しすぎてしまうと、他との競合にさらされるという危険があるのでやりたくないというならば、統合Processorの明日はないように思います。現時点では、統合のメリットなるべきものが逆にデメリットとなっているので、それを解消する方策を採れば、結果的に市場がさらに広がると思えてならないのですが、さて。(2000/8/29)

巻頭言 440「Timna、ロードマップから消える」

それはあまりに唐突だった。

いや、既に予期されていたのかも知れない。

日経BizTechニュースが昨日報じたところによると、「Intel、2度の失敗で「Timna」の出荷断念へ」によれば、PCメーカに対するロードマップからTimnaが削除されていたということのようだ。なお、このニュースではMPT(Memory Protocol Translator)チップの開発に失敗したという言及があるが、これは定かではない。

さて、ここでTimnaの位置付けを再検討してみよう。Timnaのコンセプトは低価格PC向けのプロセッサ兼チップセット、つまり統合プロセッサ(統合チップセット)として開発が進められていた。統合プロセッサについての検討は、最近では巻頭言 429 「統合チップセット話 前編」及び巻頭言 430 「統合チップセット話 後編」で取り上げているように、チップを統合することでハードウェアのコスト削減にはつながるものの、その周辺サポート(特にドライバ開発)は必要以上にコストがかかり、それが非常に重要視されるものであります。つまり、開発する側のコストというのは、統合プロセッサの開発に加えて周辺サポートのドライバなども含めた大掛かりなものとなり、一朝一夕にはできないといっていいでしょう。また、PCの更新頻度は高く、それにあわせるのも統合プロセッサには荷が重いものであることは、これも以前の巻頭言でふれたとおりです。

このように思いのほかコストのかかる統合プロセッサのメリットはどこにあるのかといえば、一般的に言われていることとして、

- ハードウェアのコストが削減される

- ハードウェアの設計が簡単(単純)になる

- ハードウェアの省スペース化が可能になる

というものがありますが、PCにとってはなかなか当てはまるものではありません。

ハードウェアのコストが削減されるというのは、まずPCを構成するチップ数が減ることで、購入するチップ数が減少するから安くなるというのは単なる思い過ごしです。安いチップを組み合わせて購入する価格と統合プロセッサ一つを購入する価格を比較して、どちらが安いかというのを検討しなければまったく無意味でしょう。むしろ、ハードウェアコストの削減というのは、部品レベルのそれよりもハードウェアの設計が簡単になるという方面からのアプローチからであり、これは即ち、「ハードウェアの設計が簡単になる」というものが統合プロセッサの大きなメリットということです。もう一方の省スペースについては、統合プロセッサのメリットではあるものの、これが即、低価格向けPCとは結びつかないことから、あとでふれることとしましょう。

Timnaが低価格PCとして位置付けられたのは、統合プロセッサとしてのメリットである「ハードウェアの設計が簡単になる」というものにほかならないはずです。そのため、今となっては非現実的な選択肢であったメモリサブシステムにDirect Rambus DRAMを採用したというのも当然でしょう。Direct Rambus DRAMは、Timna設計当時ではSDRAM等と比べて、ハードウェアが単純になる(実設計は仕様どおりに行えばノートラブルとか、配線周りの少なさ、実装スペースの優位性等)と盛んに喧伝されていたからです。ところが、ハードウェアメーカがいくら作るのが単純になったとしても、その供給元の開発能力がおぼつかないのでは本末転倒となります。ハードウェアが単純になるはずだったDirect Rambus DRAMは、様々な理由(とても一言では言い尽くせない)によって実装が大変難しく、固定されたハードウェア(一切拡張を認めない閉じたハードウェア構成)でなければ、その実力すら発揮できないことも分かってきました。要するに、リファレンスモデルの設計に並々ならぬ時間と費用をかけなければ、供給を受けるPCメーカ側の「ハードウェアの設計が簡単になる」という目的が実現できないことに加え、設計の自由度が失われたリファレンスモデルではメーカの独自性を発揮することもままならないという結果を生むわけです。

仮に、Direct Rambus DRAMが低価格で供給されるようになり、Timnaシステムに実装することに問題がなかったとしても(MPTが不要だったとしても)、上記でふれたような統合プロセッサを作るという手間と、それをリファレンスモデルに閉じ込めるという手間は何も変わるものではありません。成長を続けるハードウェアと、それとは別の更新頻度が激しいソフトウェア(特にOS)がある世界で、そのいずれもを実現するということは、困難というよりは不可能だといっていいでしょう。PCでは、統合プロセッサは時期尚早であり、これを低価格向けにフォーカスするということは、はっきりいって商売にならないというのが結論になると考えるのです。

もし、Timnaが日経BizTechニュースのいうような「MPTチップの開発に失敗」したことが原因であるのなら、Timnaシリーズすべてがキャンセルになるということはあり得ません。もちろん、このことが事実であったとしても、Timnaの消滅はそんな単純なことではなく、この項でも検討したような、あるいはもっと別の何かが原因であるのは確かでしょう。その別の原因とは、ずばり「ハードウェアの省スペース化が可能になる」という用途で方針変更があったからと見ます。ハードウェアの省スペース化でメリットがあるのは、Mobile向けプロセッサであるのは言を待ちません。Timnaの派生バージョンとしてMobile Timna(Mobile Timna+)といったものが俎上に上がっていたことは当然ですが、これが方針転換で消えたということがTimnaそのものが消えたという直因と考えるのです。

Timnaが低価格向けとしてだけであれば、MTH(Memory Translator Hub)に問題が出た時点で消えるべき存在だったでしょう。それが、ここまで長らえたのはおそらくMobile向け統合プロセッサとしての位置付けがあったからだと考えます。しかし、MobileではTransmeta社のCrusoeの登場によって明らかに現在の方向性が誤ったものだとIntelに気付かせるものとなったはずです。そうなれば、現在の延長線上にあるMobile Timnaは存在価値を失い、Crusoe対抗のMobileプロセッサ(統合プロセッサも含む)を用意する必要から、Timnaの命運は絶たれたというわけです。つまり、Timnaは間接的にCrusoeに敗れたと見ることができるのです。

それにしても、i486SLの失敗と同様の運命をたどると思っていたTimnaですが、出荷前にコケるとは…。結果として出荷前でよかったのかもしれないが…、さて。(2000/9/30)

と振り返りはここまで。Sandy BridgeはTimnaとは周辺環境が大きく変わっており、おそらくは革新的な製品となるだろう。だが、いきなりこういうものが登場するのではなく、約10年以上前のTimnaという経験があって今があるというわけである。

最近のコメント